3DIMC: bộ nhớ 3D-stacked mới nhanh gấp 10 lần HBM cho AI inference

Giới thiệu công nghệ 3DIMC của d-Matrix

d-Matrix vừa tiết lộ công nghệ Digital In-Memory Compute 3D (3DIMC), nhằm giải quyết bài toán độ trễ và chi phí năng lượng trong inference AI.

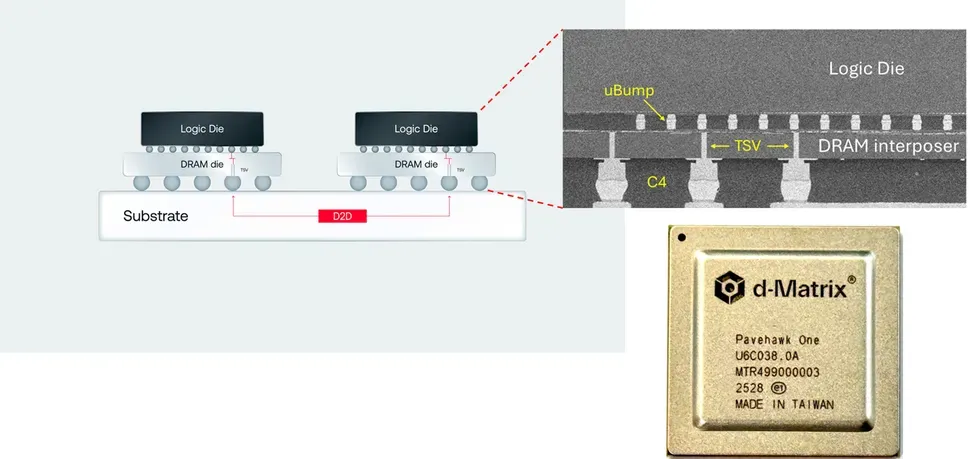

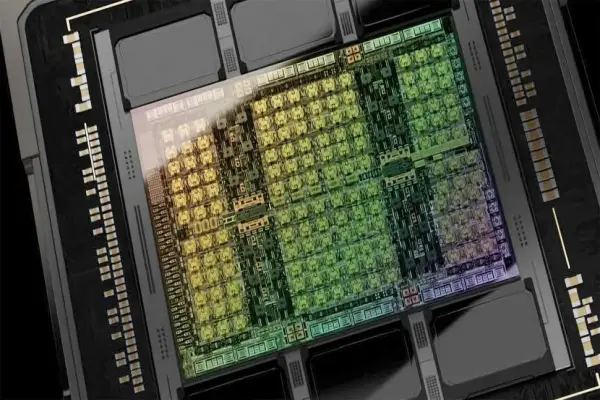

Thiết kế Pavehawk 3DIMC đang được thử nghiệm ở phòng lab, sử dụng die bộ nhớ LPDDR5 cùng các chiplet DIMC được xếp chồng qua một interposer để thực hiện các phép tính ngay trong vùng nhớ.

Điểm nổi bật kỹ thuật

DIMC logic được tối ưu cho các phép tính ma trận-vector (matrix-vector multiplication), rất phổ biến trong các mô hình transformer.

Việc “stack” bộ nhớ theo chiều dọc giúp cải thiện băng thông (bandwidth), giảm độ trễ (latency), và tăng hiệu suất sử dụng năng lượng.

Lợi thế so với HBM

d-Matrix tuyên bố rằng với 3DIMC, hiệu suất inference sẽ nhanh gấp ~10 lần so với HBM4 trong khi năng lượng tiêu thụ giảm khoảng 90%.

Ngoài ra, chi phí sản xuất có thể thấp hơn nếu có thể giảm bớt những phần “thừa” của hệ thống HBM hiện nay.

Lộ trình phát triển

Pavehawk là silicon đầu tiên hỗ trợ 3DIMC, hiện đang trong giai đoạn thử nghiệm phòng lab.

Kiến trúc thế hệ tiếp theo là Raptor, sẽ tiếp tục tích hợp 3DIMC sâu hơn nhằm tăng hiệu suất và tính khả dụng ở quy mô lớn hơn.

Thách thức & cảnh báo

Dù triển vọng hấp dẫn, nhưng công nghệ này vẫn đang trong giai đoạn đầu, chưa được chứng minh hoàn toàn trong môi trường thực tế.

Vấn đề nhiệt độ (thermal management), độ ổn định và khả năng sản xuất hàng loạt có thể là rào cản lớn.

Việc tích hợp chặt chẽ giữa bộ nhớ và logic (compute) đòi hỏi thiết kế phần cứng, đóng gói & làm mát tốt để tránh giảm hiệu suất do nóng.