PCIe 6.0 sắp thương mại hóa vào năm 2024: Alphawave xác thực tính tương thích

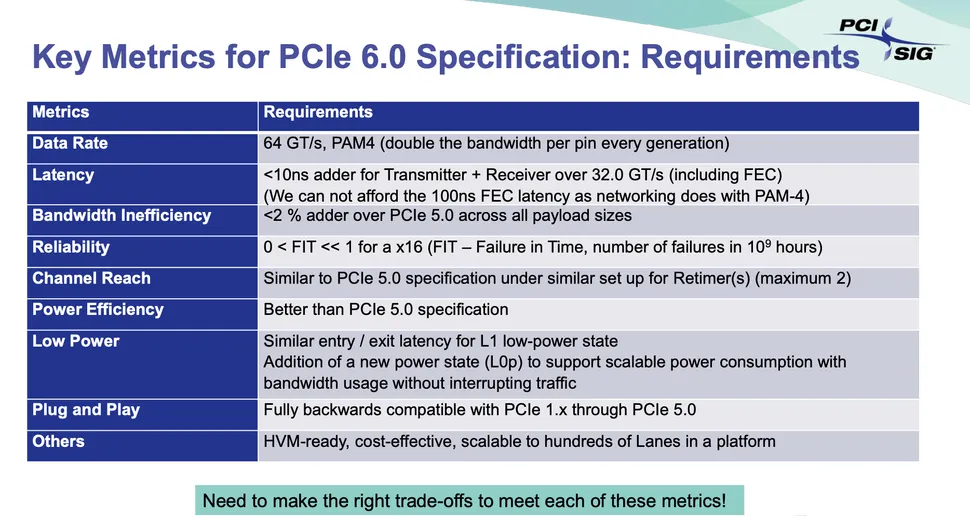

Alphawave, một nhà cung cấp IP chip và thiết kế hợp đồng (contract chip designer), đã kết hợp với Keysight để chứng minh tính tương thích (interoperability) của bộ điều khiển (controller) và giao diện vật lý (PHY) PCIe 6.0 với thiết bị kiểm thử của Keysight ở tốc độ truyền dữ liệu 64 GT/s, dấu hiệu rõ ràng cho thấy ngành đang tiến gần tới việc thương mại hóa PCIe 6.0 trong năm 2024. Bản triển khai của Alphawave không chỉ đáp ứng được PCIe 6.0 interface mà còn hỗ trợ CXL 2.0, điều mà trước đây ít được tích hợp đầy đủ trong các thử nghiệm tương tự. Giao thức mới cũng hỗ trợ các tính năng quan trọng như Forward Error Correction (FEC), chế độ FLIT, và tín hiệu PAM4 (Pulse Amplitude Modulation với 4 mức). Thêm vào đó, nền tảng của PCIe Gen6 do Alphawave phát triển có thể được mở rộng để hỗ trợ CXL 3.0 trong tương lai.

Trong quá khứ, Synopsys – cũng là một nhà cung cấp IP – đã cung cấp gói IP PCIe 6.0 (controller + PHY) từ năm 2021, và đã thực hiện thử nghiệm tương thích của giải pháp Gen6 với chip thử nghiệm của Intel. Nhưng bản demo của Alphawave đánh dấu lần đầu tiên có kết hợp thành công PCIe 6.0 & CXL 2.0 ở tốc độ cao với các đặc tính mới, cho thấy họ đã sẵn sàng để chế tạo chip có giao diện PCIe 6.0. Alphawave cũng nhấn mạnh rằng thiết kế của họ có độ trễ thấp, hiệu suất năng lượng tốt và dựa trên công nghệ PAM4 SerDes vốn đã được sử dụng thành công trong các hệ thống khác.

Với việc thử nghiệm thành công các thành phần chủ chốt như controller & PHY, tương thích với thiết bị kiểm thử bên ngoài, cộng với hỗ trợ chuẩn CXL 2.0, ngành công nghiệp phần cứng đang tiến gần tới việc có những thiết bị thương mại đầu tiên sử dụng PCIe 6.0 vào năm 2024, đặc biệt trong SSD, thiết bị mạng và các hệ thống máy chủ hiệu năng cao.